Engineering 77 Lab 5

Eight Input AND Gate

Aron Dobos, Tyler Strombom

8 November 2005

Abstract

Three implementations of an 8 input AND gate were simulated to observe differences in dynamic behavior. The three implementations are included for reference below.

Figure 0. NAND8 Implementations A, B, and C

Part 1: Testing the Implementations

It is verified below in simulation that the three different implementations give the correct output for a given input.

Figure 1. Test Circuit Schematic

Figure 2. Part 1 Simulation Results

Part 2: Counting the

Transistors

For implementation A, the eight input nand gate requires sixteen transistors and the inverter requires two transistors for a total of eighteen transistors. For implementation B, each four input nand gate requires eight transistors and the two input nor gate requires four transistors for a total of twenty transistors. For implementation C, there are five nand gates and two nor gates and each gate requires four transistors. The inverter requires two transistors for a total thirty transistors. Implementation A requires the smallest number of transistors.

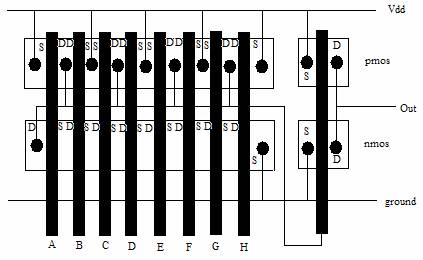

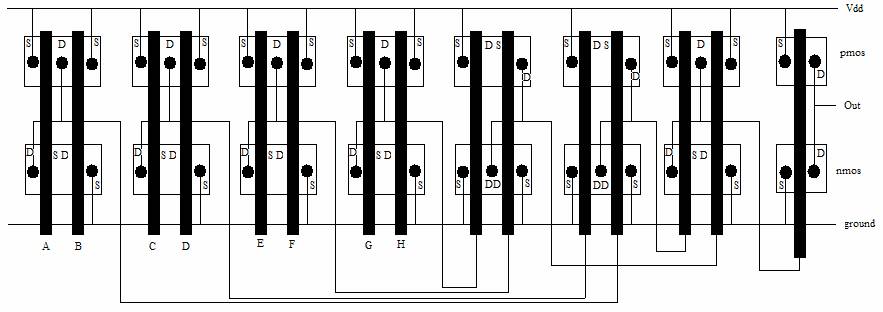

Part 3: Stick Figures

Figure 3. Implementation A

Figure 4. Implementation B

Figure 5. Implementation C

Part 4: Speed

Estimations

The following Matlab script was used to estimate the speed of each implementation.

%obtained

from Spice Netlist

cox=3.97*8.85e-14*100/(418e-10);

wn=3e-6;

wp=6e-6;

ld=.25e-6;

Keqhl=(-2*sqrt(.8))*(sqrt(.8+5)-sqrt(.8+2.5))/-2.5;

Keqlh=(-2*sqrt(.8))*(sqrt(.8+2.5)-sqrt(.8))/-2.5;

An=66e-12;

Ap=30e-12;

Cjn=8.9979e-5;

Cjp=2.9813e-4;

Cjswn=5.5248e-10;

Cjswp=3.0021e-10;

Pn=48e-6;

Pp=22e-6;

Vdd=5;

kn=5.048e-5;

kp=1.908e-5;

Vtn=.858153;

Vtp=-.889271;

wln=3/2;

wlp=3;

%calculated

using equations from book

Cgdn=cox*wn*ld;

Cgdp=cox*wp*ld;

Cdbn=An*Cjn*Keqhl+Pn*Cjswn*Keqhl;

Cdbp=Ap*Cjp*Keqlh+Pp*Cjswp*Keqlh;

Cload=Cgdn+Cgdp+Cdbn+Cdbp;

tphl=Cload/(kn*wln*(Vdd-Vtn))*((2*Vtn/(Vdd-Vtn))+log((4*(Vdd-Vtn)/Vdd)-1));

tplh=Cload*((2*Vtp/(Vdd-Vtp))+log((4*(Vdd-Vtp)/Vdd)-1))/(kp*wlp*(Vdd-Vtp));

tdelay=(tphl+tplh)/2;

%n input

propagation delay time = (n^2+n)*(delay time of inverter)

Adelay=(8^2+8)*tdelay

Bdelay=((4^2+4)+(2^2+2))*tdelay

Cdelay=((2^2+2)+(2^2+2)+(2^2+2)+1)*tdelay

The delay time for implementation A is 6.5160 ns. The delay time for implementation B is 2.3530 ns. The delay time for implementation C is 1.7195 ns.

Part 5: SPICE

Modeling

The SPICE netlists are included in Appendix A. The netlist was generated in Multisim, and then modified to change the device models and to setup the simulation for WinSpice. The circuit schematics are included in Appendix B.

e. All inputs change simultaneously.

Figure 6. Implementation A Transient Response Part E

Figure 7. Implementation B Transient Response Part E

Figure 8. Implementation C Transient Response Part E

f. All inputs but the highest one are high, and it alone is varying.

Figure 9. Implementation A Transient Response Part F

Figure 10. Implementation B Transient Response Part F

Figure 11. Implementation C Transient Response Part F

g. All inputs but the lowest one are high, and it alone is varying.

Figure 12. Implementation A Transient Response Part G

Figure 12. Implementation B Transient Response Part G

Figure 13. Implementation C Transient Response Part G

h. Comparison of results.

The results look fine. For the test when all inputs are raised, circuit B seems to be the fastest. Circuit A has lots of resistance so it charges the load capacitance more slowly, and circuit C has so many layers that the propagation delays between input and output probably dominate the response. As a result circuit B has the best balance of output resistance and short signal path for this simulation.

In the next simulation, all the inputs but the highest one were high, and it alone varied. Circuits A and B were nearly identical in speed, with circuit C being the slowest, again probably due to propagation delays between the numerous stages. The reason that circuit A could perform faster in this test was that the lower transistors were already on, so the delays associated with charging the parasitic capacitances in the lower transistors were not an issue, and only the parasitics of the top transistor were in effect.

In the last simulation, all the inputs but the lowest were high, and it alone varied. In this case circuit A was by far the slowest, probably due to the fact that charging the load capacitance had to be through all of the drain-source on-resistances of the upper transistors as well as the lowest one when it turned on.

Part 6: L-Edit Layout for Implementation 1 Based on Stick Figure

Figure 14. NAND8 implementation in L-Edit based on Stick Figure

Appendix A SPICE Netlists

Device Models

.MODEL MNMOSIS NMOS LEVEL=2 LD=0.250000U TOX=418.000008E-10

+ NSUB=9.236187E+14 VTO=0.858153 KP=5.048000E-05 GAMMA=0.198

+ PHI=0.6 UO=596.729 UEXP=7.029586E-02 UCRIT=10266.7

+ DELTA=2.7371 VMAX=65701.4 XJ=0.250000U LAMBDA=1.843384E-02

+ NFS=1.086360E+12 NEFF=1 NSS=1.000000E+10 TPG=1.000000

+ RSH=28.760000 CGDO=3.097916E-10 CGSO=3.097916E-10 CGBO=3.838441E-10

+ CJ=8.997900E-05 MJ=0.783638 CJSW=5.524800E-10 MJSW=0.285064 PB=0.800000

.MODEL MPMOSIS PMOS LEVEL=2 LD=0.250000U TOX=418.000008E-10

+ NSUB=9.309300E+15 VTO=-0.889271 KP=1.908000E-05 GAMMA=0.6289

+ PHI=0.6 UO=216.28 UEXP=0.218144 UCRIT=62664

+ DELTA=0.164572 VMAX=100000 XJ=0.250000U LAMBDA=5.011626E-02

+ NFS=9.266623E+11 NEFF=1.001 NSS=1.000000E+10 TPG=-1.000000

+ RSH=66.820000 CGDO=3.097916E-10 CGSO=3.097916E-10 CGBO=3.727276E-10

+ CJ=2.981300E-04 MJ=0.556944 CJSW=3.002100E-10 MJSW=0.243045 PB=0.800000

Part

** and_A **

* all PMOS bulk tied to VDD

* all NMOS bulk tied to GND

MQ18 Vout NotVout VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ17 Vout NotVout 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

VDDVDD VDD 0 dc 5

MQ16 7 In 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ15 6 In 7 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ14 5 In 6 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ13 4 In 5 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ12 3 In 4 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ11 2 In 3 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ10 1 In 2 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ9 NotVout In 1 1 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ8 NotVout In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ7 NotVout In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ6 NotVout In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ5 NotVout In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ4 NotVout In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ3 NotVout In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ2 NotVout In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ1 NotVout In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

Vin In 0 pulse(0 5 1ns 0 0 20ns)

*V1 (initial value)

*V2 (pulsed value)

*TD (delay time)

*TR (rise time)

*TF (fall time)

*PW (pulse width)

*PER(period)

.control

tran .5ns 30ns

* step end

plot V(In) V(Vout)

.endc

.end

Part

** and_B **

* all PMOS bulk tied to VDD

* all NMOS bulk tied to GND

MQ20 Vout 14 4 VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ19 4 8 VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ8 8 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ16 14 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ15 14 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ14 14 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ13 14 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ5 8 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ6 8 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ7 8 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ18 Vout 14 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ17 Vout 8 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ4 3 In 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ12 12 In 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ11 11 In 12 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ10 10 In 11 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ9 14 In 10 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ1 8 In 1 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ2 1 In 2 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ3 2 In 3 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

VDDVDD VDD 0 dc 5

Vin In 0 pulse(0 5 1ns 0 0 20ns)

*V1 (initial value)

*V2 (pulsed value)

*TD (delay time)

*TR (rise time)

*TF (fall time)

*PW (pulse width)

*PER(period)

.control

tran .5ns 30ns

* step end

plot V(In) V(Vout)

.endc

.end

Part

** and_C **

* all PMOS bulk tied to VDD

* all NMOS bulk tied to GND

MQ30 NotVout nor1_out VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ29 NotVout nor2_out VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ15 nand4_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ16 nand4_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ12 nand3_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ26 Vout NotVout VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ20 nor1_out nand2_out 4 VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ19 4 nand1_out VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ11 nand3_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ8 nand2_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ7 nand2_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ3 nand1_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ4 nand1_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ24 nor2_out nand4_out 17 VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ23 17 nand3_out VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ28 NotVout nor2_out 2 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ27 2 nor1_out 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ13 13 In 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ14 nand4_out In 13 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ25 Vout NotVout 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ22 nor2_out nand4_out 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ21 nor2_out nand3_out 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ18 nor1_out nand2_out 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ17 nor1_out nand1_out 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ10 nand3_out In 9 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ9 9 In 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ6 nand2_out In 5 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ5 5 In 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ1 1 In 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ2 nand1_out In 1 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

VDDVDD VDD 0 dc 5

Vin In 0 pulse(0 5 1ns 0 0 20ns)

*V1 (initial value)

*V2 (pulsed value)

*TD (delay time)

*TR (rise time)

*TF (fall time)

*PW (pulse width)

*PER(period)

.control

tran .5ns 30ns

* step end

plot V(In) V(Vout)

.endc

.end

Part F NAND8

Implementation A

** and_A **

* all PMOS bulk tied to VDD

* all NMOS bulk tied to GND

MQ18 Vout NotVout VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ17 Vout NotVout 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

VDDVDD VDD 0 dc 5

MQ16 7 VDD 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ15 6 VDD 7 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ14 5 VDD 6 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ13 4 VDD 5 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ12 3 VDD 4 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ11 2 VDD 3 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ10 1 VDD 2 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

* only topmost transistor pair is changing

MQ9 NotVout In 1 1 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ8 NotVout In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ7 NotVout VDD VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ6 NotVout VDD VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ5 NotVout VDD VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ4 NotVout VDD VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ3 NotVout VDD VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ2 NotVout VDD VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ1 NotVout VDD VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

Vin In 0 pulse(0 5 1ns 0 0 20ns)

*V1 (initial value)

*V2 (pulsed value)

*TD (delay time)

*TR (rise time)

*TF (fall time)

*PW (pulse width)

*PER(period)

.control

tran .5ns 30ns

* step end

plot V(In) V(Vout)

.endc

.end

Part F NAND8

Implementation B

** and_B **

* all PMOS bulk tied to VDD

* all NMOS bulk tied to GND

MQ20 Vout 14 4 VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ19 4 8 VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ16 14 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ15 14 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ14 14 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ13 14 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ5 8 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ6 8 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ7 8 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ8 8 VChanging VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ1 8 VChanging 1 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ18 Vout 14 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ17 Vout 8 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ4 3 In 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ12 12 In 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ11 11 In 12 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ10 10 In 11 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ9 14 In 10 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ2 1 In 2 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ3 2 In 3 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

VDDVDD VDD 0 dc 5

Vin In 0 DC 5

Vinput Vchanging 0 pulse(0 5 1ns 0 0 20ns)

*V1 (initial value)

*V2 (pulsed value)

*TD (delay time)

*TR (rise time)

*TF (fall time)

*PW (pulse width)

*PER(period)

.control

tran .5ns 30ns

* step end

plot V(Vchanging) V(Vout)

.endc

.end

Part F NAND8

Implementation C

** and_C **

* all PMOS bulk tied to VDD

* all NMOS bulk tied to GND

MQ30 NotVout nor1_out VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ29 NotVout nor2_out VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ15 nand4_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ16 nand4_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ12 nand3_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ26 Vout NotVout VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ20 nor1_out nand2_out 4 VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ19 4 nand1_out VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ11 nand3_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ8 nand2_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ7 nand2_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ3 nand1_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ24 nor2_out nand4_out 17 VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ23 17 nand3_out VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ4 nand1_out VChanging VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ2 nand1_out VChanging 1 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ28 NotVout nor2_out 2 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ27 2 nor1_out 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ13 13 In 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ14 nand4_out In 13 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ25 Vout NotVout 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ22 nor2_out nand4_out 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ21 nor2_out nand3_out 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ18 nor1_out nand2_out 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ17 nor1_out nand1_out 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ10 nand3_out In 9 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ9 9 In 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ6 nand2_out In 5 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ5 5 In 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ1 1 In 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

VDDVDD VDD 0 dc 5

Vin In 0 dc 5

Vpulse VChanging 0 pulse(0 5 1ns 0 0 20ns)

*V1 (initial value)

*V2 (pulsed value)

*TD (delay time)

*TR (rise time)

*TF (fall time)

*PW (pulse width)

*PER(period)

.control

tran .5ns 30ns

* step end

plot V(VChanging) V(Vout)

.endc

.end

Part G NAND8

Implementation A

** and_A **

* all PMOS bulk tied to VDD

* all NMOS bulk tied to GND

MQ18 Vout NotVout VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ17 Vout NotVout 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

VDDVDD VDD 0 dc 5

MQ15 6 In 7 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ14 5 In 6 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ13 4 In 5 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ12 3 In 4 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ11 2 In 3 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ10 1 In 2 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ9 NotVout In 1 1 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ16 7 VChanging 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ1 NotVout VChanging VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ8 NotVout In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ7 NotVout In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ6 NotVout In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ5 NotVout In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ4 NotVout In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ3 NotVout In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ2 NotVout In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

Vin In 0 dc 5

Vpulse VChanging 0 pulse(0 5 1ns 0 0 20ns)

*V1 (initial value)

*V2 (pulsed value)

*TD (delay time)

*TR (rise time)

*TF (fall time)

*PW (pulse width)

*PER(period)

.control

tran .5ns 30ns

* step end

plot V(VChanging) V(Vout)

.endc

.end

Part G NAND8

Implementation B

** and_B **

* all PMOS bulk tied to VDD

* all NMOS bulk tied to GND

MQ20 Vout 14 4 VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ19 4 8 VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ8 8 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ16 14 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ15 14 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ14 14 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ13 14 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ6 8 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ7 8 In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ4 3 VChanging 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ5 8 VChanging VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ18 Vout 14 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ17 Vout 8 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ12 12 In 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ11 11 In 12 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ10 10 In 11 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ9 14 In 10 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ1 8 In 1 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ2 1 In 2 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ3 2 In 3 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

VDDVDD VDD 0 dc 5

Vin In 0 dc 5

Vpulse VChanging 0 pulse(0 5 1ns 0 0 20ns)

*V1 (initial value)

*V2 (pulsed value)

*TD (delay time)

*TR (rise time)

*TF (fall time)

*PW (pulse width)

*PER(period)

.control

tran .5ns 30ns

* step end

plot V(VChanging) V(Vout)

.endc

.end

Part G NAND8

Implementation C

** and_C **

MQ30 NotVout nor1_out VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ29 NotVout nor2_out VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ15 nand4_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ16 nand4_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ12 nand3_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ26 Vout NotVout VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ20 nor1_out nand2_out 4 VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ19 4 nand1_out VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ11 nand3_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ8 nand2_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ7 nand2_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ4 nand1_out In VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ24 nor2_out nand4_out 17 VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ23 17 nand3_out VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ3 nand1_out VChanging VDD VDD MPMOSIS L=2u W=6u AD=30p PD=22u AS=12p PS=16u

MQ1 1 VChanging 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ28 NotVout nor2_out 2 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ27 2 nor1_out 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ13 13 In 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ14 nand4_out In 13 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ25 Vout NotVout 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ22 nor2_out nand4_out 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ21 nor2_out nand3_out 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ18 nor1_out nand2_out 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ17 nor1_out nand1_out 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ10 nand3_out In 9 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ9 9 In 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ6 nand2_out In 5 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ5 5 In 0 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

MQ2 nand1_out In 1 0 MNMOSIS L=2u W=3u AD=66p PD=48u AS=78p PS=52u

VDDVDD VDD 0 dc 5

Vin In 0 dc 5

Vpulse VChanging 0 pulse(0 5 1ns 0 0 20ns)

.control

tran .5ns 30ns

* step end

plot V(VChanging) V(Vout)

.endc

.end

Appendix

B Multisim Schematics for Netlist Generation.

Figure B1. Implementation A

Figure B2. Implementation B.

Figure B3. Implementation C